Flip-flops are bistable devices, which means there are two stable states. The flip-flop is a combination of latches, the only difference between a latch and a flip-flop is that the clock triggering occurs in the case of a flip-flop. A latch is a level-triggered device, and a flip-flop is an edge-triggered device.

Conversion of Flip-flops

Conversion of flip-flop means the conversion of one form of flip from one form to another form, for example, conversion from JK flip-flop to T-flip-flop and other conversion.

- SR flip-flop to JK flip-flop

- JK flip-flop to SR flip-flop

- SR flip-flop to D flip-flop

- D flip-flop to SR flip-flop

- JK flip-flop to T flip-flop

- JK flip-flop to D flip-flop

- D flip-flop to JK flip-flop

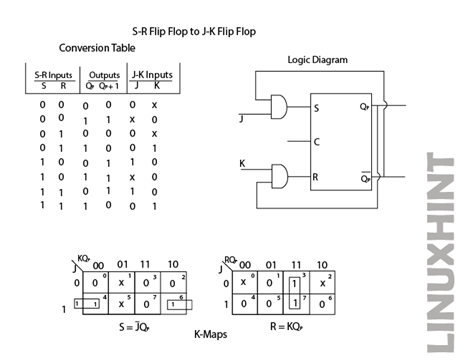

SR flip-flop to JK Flip-flop

Below, the given figure shows that the output of JK is given as input to the SR flip-flop. The conversion table is given in which Qp is the present state and Qp+1 is the next state of the flip-flop. For two inputs, there are eight outputs. The K-map for this conversion is also given in the below figure, this K-map shows the possible stable states of JK flip-flop.

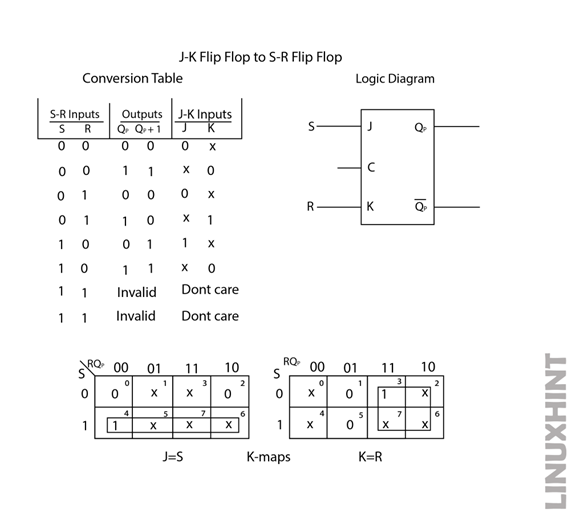

JK flip-flop to SR flip-flop

Below given figure shows the output of SR given as input to the JK flip-flop. This conversion is just opposite to the above-given conversion. The conversion table is given, in which Qp is the present state and Qp+1 is the next state of the flip-flop. For two inputs, there are eight outputs, and the K-map for this conversion is also given in the below figure. The K-map for only the invalid state of the SR flip-flop is given in the figure.

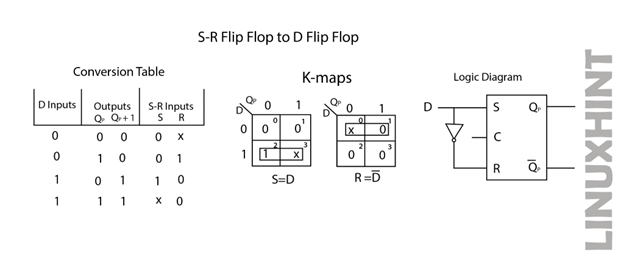

SR flip-flop to D flip-flop

Below given figure shows the conversion from SR to D flip-flop by just adding a not gate from the S to R connection. The conversion table is given in which Qp is the present state and Qp+1 is the next state of the flip-flop. For one input of D, there are four combinations made. K-map for D and D is not given in the figure.

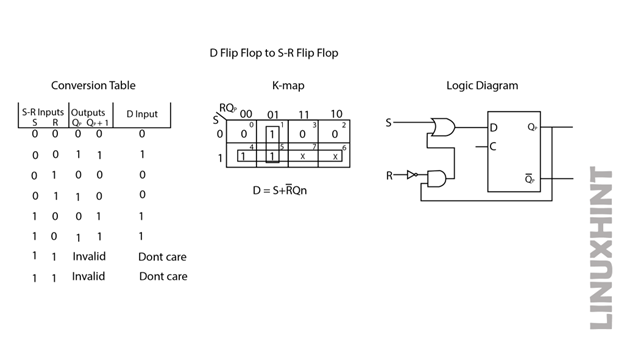

D flip-flop to SR flip-flop

SR are the external inputs to the flip-flop, S is just given as its state, but a not logic gate is used with R. For two inputs SR flip-flop there are eight combinational states. There is an invalid state in this flip-flop for which don’t care is shown in the k-map shown in the figure.

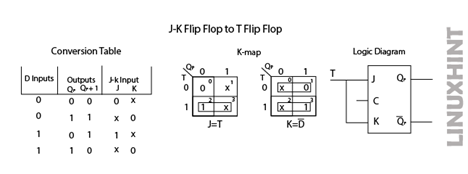

JK flip-flop to T Flip-flop

Below given figure shows the conversion from JK to T flip-flop by just connecting both the inputs of JK together. For one input of T flip-flop, there is a conversion table of four outputs shown below. K-map for both toggle and its opposite condition is also shown.

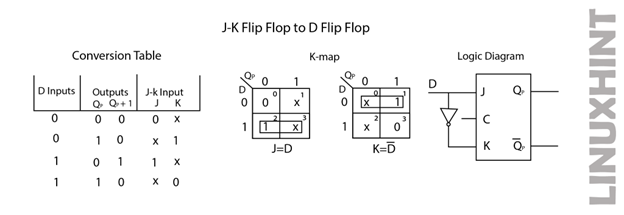

JK flip-flop to D Flip-flop

Below given figure shows the conversion of JK to D flip-flop by just connecting the JK together by a NOT logic gate. For one input of the D flip-flop, the combination table of four outputs is also given in the figure. The k-map for the D and the opposite of D is shown below:

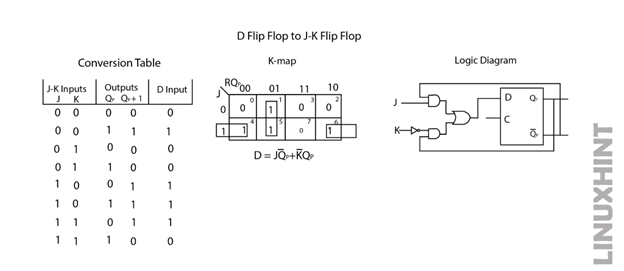

D flip-flop to JK Flip-flop

The below figure shows a clear visualization of the conversion from D to JK flip-flop. In this conversion JK is the external input to the flip flop, for two inputs of JK there are four possible combinational outputs given in the figure. The k-map for the desired out is also depicted in the figure.

Conclusion

The flip-flop is the combination of latches, the only difference between latch and flip-flop is that the clock triggering occurs in the case of the flip-flop. Conversion of flip-flop from one form to another is an easy process for example JK to T conversion, just combine both the inputs JK and make one input of T.