A text file called a “makefile” is used to store the commands for creating software projects. It automatically links, sets up, and compiles the project’s original code using a target file. A makefile is employed to create an object and target files from a source code file. Upon the execution of a target file, the code within the source code file will be executed, and your project will run in no time. Within this guide, we will give you comprehensive details about how to make a makefile using variables and arguments.

A basic makefile consists of three parts:

- The variables are labeled entities to store the project-related data.

- The rules specify how to create an intended file using the dependencies in the makefile.

- The documents that the makefile is designed to generate are referred to as targets.

Makefile Variables

As we already described, a labeled object that may be utilized to store the data is referred to as a makefile variable. A variable’s value may be a single character, a numerical value, or a collection of values. The titles of the source and target documents, as well as the instructions to be employed to create the targets, are all data regarding the build procedure that are stored in variables.

Create the Makefile Variables

To define a simple variable in makefile, we should start it with a simple title followed by the “=” sign and the value that will be stored in it:

On the other hand, it is preferred and recommended to try “:=” instead of “=” for a quick and best performance of a project.

For instance, we create a makefile for the C project and declare a “CC” variable. This variable stores the compiler that is executable for C, i.e. “gcc”, as a value. At the fourth line, we create the “CFLAGS” variable that is used to give warnings while the compilation process is happening. This is to enhance the optimization of a project that you are running and to avoid any issues.

Just like that, the “TARGET” variable in this code snippet is employed to set the new target file that is generated after the execution of a makefile. While creating a make file, it is necessary to set the source and object files after setting a target file. The source and object files can also be defined using the variables. You can name these variables as per your choice.

For example, the SRCS variable sets a source file while the OBJS variable sets a new object file using the SRCS variable.

CFLAGS = -Wall

TARGET = New

SRCS = main.c

OBJS = $(SRCS:.c=.o)

Use the Makefile Variables

After declaring or defining the makefile variables, it’s very necessary to make them useable in the makefile. To use a makefile variable, you have to utilize the “$” sign followed by the “()” or “{}” brackets. For instance, we use the “$()” to build the target executable file. After doing this step, the target file will be able to respond.

Makefile Arguments

Whenever the makefile is called, a value is supplied to it as a parameter that is known as an “argument”. The arguments are employed to override the original value of a mutable or to add more details to the makefile at runtime. To pass the command-line arguments to a variable in a makefile, you should use the “make” keyword followed by a variable name and an argument value that is passed to it:

These parameters may be accessed as ordinary variables in the makefile, i.e. “New” is the argument value of the “TARGET” variable.

Example: Make the Variables and Arguments

To demonstrate the use of variables and arguments in makefile, we use a simple example in C++. We create a new C++ file in Notepad++ and add an “iostream” header to use the input and output in a sample program.

The main() function starts with the declaration of a character type variable “v”. The standard output stream which is “cout” is used to display and ask the user for input. In contrast, the “cin” standard input stream gets an input value from a user at runtime and saves it to the “v” variable. The standard “cout” is again used to display the value that is added by a user at run-time. The “return 0” statement ends the program execution successfully.

int main() {

char v;

std::cout << "Enter a value: ";

std::cin >> v;

std::cout << v << std::endl;

return 0;

}

A makefile is generated using a standard way. The very first variable, “CXX”, declares the compiler to be used to run the C++ file, i.e. “g++”. The very next variable is used to set the flags for a compiler to avoid any issues.

Now, the target file is set using the “TARGET” variable to “New”. This is an executable file. After this, the makefile defines its source and object file via the SRCS and OBJS variables. To make use of the declared variables, we utilize the “$” sign followed by the “()” brackers to build the target executable, object file, and clean the object and target file.

CXXFLAGS = -std=c++11 -Wall

TARGET = New

SRCS = main.cpp

OBJS = $(SRCS:.cpp=.o)

all: $(TARGET)

$(TARGET): $(OBJS)

$(CXX) $(CXXFLAGS) -o $(TARGET) $(OBJS)

%.o: %.cpp

$(CXX) $(CXXFLAGS) -c $< -o $@

clean:

rm -f $(TARGET) $(OBJS)

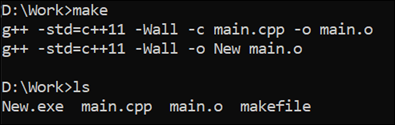

After saving the C++ and its makefile, launch the CMD of your system, navigate into the working directory, and run the make instruction as follows. It generates the “main.o” object file and the “New.exe” target file for the source code file. We haven’t passed any argument to make the instructions for now.

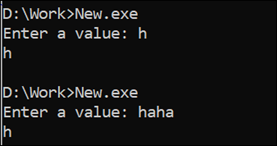

Running the target file will ask the user for input. We add the “h” character at the first execution and “haha” at the second execution. While the “v” variable only accepts the “character” values, the “h” character from the “haha” string is stored and displayed.

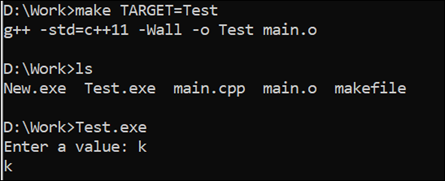

Let’s run the make instruction using the command-line arguments that are passed to the makefile variables. So, we alter the “TARGET” variable value and pass “Test” to it. After that, the “Test.exe” file is generated and works exactly like the “New.exe” file.

Test.exe

Conclusion

Within this comprehensive guide, we have gone through the contents of makefile one by one. We elaborated on how to declare the variables in a makefile, how to make them usable, and how to alter their value at runtime with the help of arguments. Supporting our explanation, we discussed a simple example in C++.